[최준호의 첨단의 끝을 찾아서] 나노종합기술원과 KAIST

대전 KAIST 캠퍼스 내에 있는 나노종합기술원의 연구원들이 12인치 반도체 테스트 베드를 활용해 제작한 40나노 패턴 웨이퍼를 선보이고 있다. 프리랜서 김성태

‘세계 파운드리(반도체 위탁생산) 1위 대만 TSMC, 타이난에 있는 공장(팹18)에 3나노 반도체 생산장비 설치 시작. 2022년 본격 양산에 돌입.’(8월4일) ‘인텔, 2024년에 2나노급 ‘20A’ 반도체 양산해 현재 앞서 있는 삼성전자와 TSMC 추월 선언.’(7월26일) ‘삼성전자, 2022년에 3나노미터 1세대 공정 양산할 계획.’(7월29일)

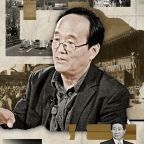

조병진 KAIST 전기 및 전자공학부 교수 인터뷰 #반도체 업계 초미세 공정 경쟁 뜨거워 #물리적으로 보는 한계는 2~3나노 #한국 정부의 연구개발 지원 모자라 #기업들이 석·박사까지 재교육시켜야

1nm(나노미터)는 10억분의 1m. 머리카락 굵기의 10만분의 1 세계다. 세계 반도체 기업들의 초미세 공정 경쟁이 뜨겁다. 이들이 파고드는 나노의 세계는 반도체 회로 선폭의 굵기를 말한다. 보다 작은 면적에 더 많은 회로를 그려 넣는 기업이 세계 반도체 시장을 석권한다.

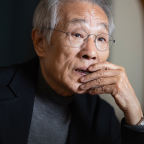

대전 KAIST 캠퍼스 안에 자리한 나노종합기술원은 국내 반도체 테스트베드의 대표적 현장이다. 실리콘 웨이퍼에 반도체 회로를 그려 내는 노광장비 등 고가의 첨단 반도체 장비 200여대와 전문인력을 보유한 국내 최대 규모의 관련 공공기관이다. 중소기업은 물론 대기업들도 실리콘 기반의 반도체를 연구·개발하기 위해 나노종합기술원을 활용하고 있다. KAIST를 비롯, 반도체를 연구하는 대학의 교수와 학생도 마찬가지다. 워낙 고가인 탓에 국내 기업과 대학들이 다양한 반도체 관련 장비를 자체적으로 모두 마련하기는 어렵다. 삼성전자의 경우에도 생산시설엔 세계 최고 수준의 장비를 갖추고 있지만, 연구개발쪽엔 부족한 부분이 있다. 지난 13일 나노종합기술원 시설을 둘러보고, 같은 건물에 연구실을 둔 조병진(58) KAIST 전기 및 전자공학부 교수를 만나 반도체 연구개발의 현주소와 미래를 물어봤다. 조 교수는 반도체 소자 전공으로, 최근에는 지능형 반도체 연구에 몰두하고 있다.

조병진 KAIST 전기 및 전자공학부 교수의 주전공은 반도체 소자다. 최근에는 지능형 반도체 연구에 몰두하고 있다. 프리랜서 김성태

- 삼성전자와 대만 TSMC를 중심으로 파운드리 경쟁이 뜨겁다. 왜 TSMC인가.

- 초기의 세계 주요 반도체 회사들은 원래 설계부터 생산까지 모든 것을 다 했다. 하지만 생산엔 어마어마한 규모의 시설이 필요했다. 그래서 생겨난 비즈니스가 파운드리, 즉 ‘반도체 위탁생산’이라는 것이다. 반도체를 설계한 뒤 소량 다품종 생산을 해야 하는 비메모리, 즉 로직소자 생산에 적합한 형태다. 대만의 모리스 창이 1987년 설립한 TSMC가 시작이었다. 한국은 처음부터 메모리로 반도체 사업을 시작했다. 비메모리, 다시 말해 로직 소자는 소규모로만 하고 있었다. 그런데 비메모리 시장은 시간이 흐를수록 더 빨리 성장했다. 인공지능(AI)으로 대표되는 4차산업혁명의 영향이 본격적이다. 현재 세계 반도체 시장에서 메모리와 비메모리가 차지하는 비율이 30대 70이다. 삼성전자는 메모리 분야에선 세계 1위이지만, 파운드리 사업은 2005년에서야 손을 대기 시작했다. 데이터를 단순히 저장하는 메모리 소자와 연산을 처리하는 비메모리의 소자는 완전히 다르다. 이 분야에서 1등을 따라잡기가 쉽지 않은 이유다.

- 왜 미세공정 경쟁을 벌이나.

- 세계 반도체 경쟁 중 대표적인 분야가 초미세 공정이다. 웨이퍼 한 장에 더 많은 반도체를 생산할 수 있으면 생산성은 높아지고 가격은 내려간다. 게다가 반도체 회로가 작을수록 소비전력은 줄어들고, 정보처리 속도는 빨라진다. 세계 주요 반도체 회사들이 초미세공정 경쟁을 벌이는 이유다. 반도체 칩 하나에는 수십억 개 이상의 트랜지스터가 들어 있다. 트랜지스터는 쉽게 말하면 껐다 켰다 할 수 있는 스위치다. 전자가 양단의 폭 사이를 지나가거나 안 지나가거나 하는 거다. 그 간격이 짧을수록 소자의 동작이 빨라진다. 연구자들은 지난 50년간 반도체를 더 작게 만들기 위해 노력해 왔다. 초미세 공정의 핵심 중 하나가 최첨단 노광장비인데, 네덜란드 ASML이 10nm 이하의 회로를 그릴 수 있는 극자외선(EUV) 노광장비를 독점생산하고 있다.

![이재용 삼성전자 부회장이 지난해 10월 네덜란드 에인트호번에 위치한 반도체 장비업체 ASML를 방문, 생산과정을 살펴보고 있다. ASML은 반도체 노광장비 전문 업체로 극자외선(EUV) 장비를 유일하게 생산하는 곳이다. 이 곳에서 이 부회장은 피터 버닝크 CEO 등을 만나 차세대 반도체 기술 개발을 위한 협력 강화 방안을 논의했다. [사진 삼성전자]](https://pds.joongang.co.kr/news/component/htmlphoto_mmdata/202108/20/532b81bd-fc0b-4af3-97b6-0ec046dc2bb8.jpg)

이재용 삼성전자 부회장이 지난해 10월 네덜란드 에인트호번에 위치한 반도체 장비업체 ASML를 방문, 생산과정을 살펴보고 있다. ASML은 반도체 노광장비 전문 업체로 극자외선(EUV) 장비를 유일하게 생산하는 곳이다. 이 곳에서 이 부회장은 피터 버닝크 CEO 등을 만나 차세대 반도체 기술 개발을 위한 협력 강화 방안을 논의했다. [사진 삼성전자]

- ASML 장비가 핵심이라면, 삼성전자와 TSMC 간 기술력 차이가 무슨 의미인가.

- 같은 초미세공정 장비를 사용하더라도 소자기술, 소재 균일도, 공정기술 등에 따라 반도체 수율의 차이가 결정된다. 반도체라는 것이 한두 개 만들기는 쉽다. 칩 하나에 트랜지스터가 현재 10억 개 이상 들어간다. 이 10억 개 이상의 트랜지스터가 균일하게 동작해야 한다. 그 칩이 웨이퍼에 최소 100개 이상 들어간다. 많이 들어가면 500개 이상 들어간다. 웨이퍼 한 장에 트렌지스터가 1조 개 들어간다는 얘기다. 한 달에 1만 장의 웨이퍼를 생산한다면 1만조 개의 트랜지스터가 균일한 동작을 해야 한다. 그만큼 어려운 기술이다.

- 어디까지 작게 만들 수 있을까.

- 미세공정에는 극복해야 할 문제가 있다. 양단의 사이가 멀면 스위치를 껐을 때 전자의 흐름이 확실히 차단이 되는데, 가까워지면 스위치를 꺼도 전자의 일부가 건너간다. 소위 ‘누설전류’라 부르는 거다. 가까워질수록 완전히 차단하기 어려워진다. 즉 끈 상태인 0과 켠 상태인 1의 정확한 구분이 안 될 수 있다. 누설전류가 많으면 대기 상태의 전력소모도 많아진다. 트랜지스터가 제대로 동작할 수 있는 한계가 예전 1980년대에는 100나노라고 얘기했다가, 90년대 와서는 50나노 정도라고 했다. 하지만 기술 발달이 그 한계를 계속 극복해 왔다. 이제는 5나노, 3나노를 얘기하고 있다. 지금에 생각해 보면 100나노는 운동장이다. 학계에서 트랜지스터의 물리적인 사이즈의 한계를 2~3나노라고 본다. 이제 세계는 반도체 소자를 작게 만드는 기술은 한계에 거의 도달했다고 본다.

![파운드리 분야 세계 1위인 대만의 TSMC 본사 앞을 한 행인이 지나가고 있다. [AFP=연합뉴스]](https://pds.joongang.co.kr/news/component/htmlphoto_mmdata/202108/20/8d683839-f901-4c34-8ed2-63302e99e92d.jpg)

파운드리 분야 세계 1위인 대만의 TSMC 본사 앞을 한 행인이 지나가고 있다. [AFP=연합뉴스]

- 그간 한계를 어떻게 극복해왔나.

- 노광장비의 발전도 있었지만, 트랜지스터 구조에도 획기적인 혁신이 있었다. 버클리대 첸밍후 교수의 연구를 바탕으로 2011년 인텔이 22nm에서 핀펫(FinFETㆍFin field-effect transistor) 구조를 도입하면서 한계를 한 차례 돌파했다. 이후 회로의 선폭은 점점 더 작아졌다.앞으로 또 어디까지 더 내려갈지는 알 수 없다. 하지만 반도체 회사들이 3nm 기술이라고 부르는 게 물리적 사이즈가 3nm라는 뜻은 아니다. 하나의 상징적인 이름이다. 20nm 부근부터 크기를 줄이지 않아도 성능이 개선되면 그런 식으로 낮춰 부르고 있다. 요즘 터보엔진 승용차에서 실제 배기량과 모델 표기가 다른 것이 비슷한 사례다. TSMC에서 2~3nm 기술이라고 부를 때 실제 트랜지스터의 물리적 사이즈는 5nm 정도일 거다.

- 앞으로도 더 진화할 수 있을까.

- 이제 연구자들이 다른 방법을 통해 반도체의 성능을 개선하는 연구를 하기 시작했다. 예를 들면 우리 연구실에선 ‘모놀리틱 3D(M3D) 집적기술’이라는 것도 하고 있다. 반도체 칩이란 게 실리콘 웨이퍼 위에 소자를 만들고, 금속 배선을 연결하는 건데, 지금까지는 이걸 보다 더 작게 만들려고 애썼다. M3D 집적기술은 실리콘 웨이퍼에 소자를 만들고 연결한 뒤 그 위에 다시 얇은 실리콘을 또 붙이고 소자를 만드는 방식이다. 이렇게 2층, 3층의 소자를 만드는 거다. TSMC도 이걸 활발하게 연구하고 있다. 이 외에도 전기 대신 자기 스위치를 쓰는 스핀 소자 등 새로운 개념들이 연구되고 있다.

![문재인 대통령이 지난 5월 ‘K반도체 전략 보고’ 참석자와 기념촬영하고 있다. 왼쪽부터 공영운 현대차 사장, 이현덕 원익IPS 대표, 유은혜 교육부 장관, 최시영 삼성전자 파운드리 사장, 문 대통령, 이재명 경기지사, 문승욱 산업통상자원부 장관, 이정배 삼성전자 메모리 사장. [청와대사진기자단]](https://pds.joongang.co.kr/news/component/htmlphoto_mmdata/202108/20/0acb7377-3c49-49e7-a784-347b6ba71e7c.jpg)

문재인 대통령이 지난 5월 ‘K반도체 전략 보고’ 참석자와 기념촬영하고 있다. 왼쪽부터 공영운 현대차 사장, 이현덕 원익IPS 대표, 유은혜 교육부 장관, 최시영 삼성전자 파운드리 사장, 문 대통령, 이재명 경기지사, 문승욱 산업통상자원부 장관, 이정배 삼성전자 메모리 사장. [청와대사진기자단]

- 국내에 반도체 연구인력이 부족하다고 들었다. 왜인가.

- 정부에서 꽤 오랫동안 대학에서의 실리콘 반도체 연구개발(R&D) 지원을 제대로 해 주질 않았다. 기업에서 잘하고 있으니 정부가 굳이 나서야 하느냐는 생각이었을 것이다. 한동안 과기부 R&D 과제 공모에 실리콘 반도체 연구 분야 자체가 없었다. 그래서 실리콘 반도체를 전공은 많은 연구자가 다른 분야를 연구할 수밖에 없었다. 당연히 대학에서도 그런 연구자를 잘 뽑지 않았고, 따라서 대학원생들도 없었다. 그 결과 반도체 연구자들의 수가 크게 줄었다. 삼성전자에서 반도체를 전공한 인력을 뽑고 싶어도 사람이 없다. 그러다 보니 전공에 관계없이 공대를 졸업한 사람이면 아무나 뽑아 재교육을 시키고 있는 실정이다. 요즘은 원자력을 전공한 학생들도 갈 곳이 없어 삼성전자에 지원한 경우들이 있다.

- 그래도 한국이 메모리 분야에선 세계 1위 아닌가.

- 지금 한국의 반도체를 이끌고 있는 50~60대는 대학 입학 당시 최고의 인재들이었다. 전자과가 의대보다 높던 시절도 있었다. 안타까운 일이지만 80년대에 반도체를 전공한 학생들과 지금 학생들은 여러모로 차이가 크다. 지금은 전국 의대 다 돌고서야 서울대 공대나 KAIST로 오고 있지 않나. 이게 당장은 몰라도 20~30년 뒤엔 표시가 난다. 지금처럼 가면 다음 세대 한국 반도체는 현재 위치를 보장할 수 없다. 최근에 와서 다시 반도체가 중요하다고 하니 반도체학과를 만드는 등 지원을 늘리고 있다. 운동경기처럼 산업도 한 분야에서 잘하려면 선수층이 두터워야 한다. 현재 우리나라 수출에서 반도체가 20% 이상을 차지한다는 점을 고려해야 한다. 지금도 늦지 않았다.

사실 연구인력만 부족한 게 아니다. 공공기관 중에선 국내에서 유일하게 실리콘 기반 ‘첨단 반도체 장비’를 보유하고 있다는 나노종합기술원에는 지난 3월부터 20nm 수준의 반도체 회로를 그릴 수 있는 노광장비 ArF 이머전 스캐너를 가동하기 시작했다. 삼성전자가 10여 년 동안 쓰던 중고장비를 어렵게 인수한 거다. 지난해까지는 2009년 하이닉스에서 받아온 180nm 급 KrF 스캐너를 썼다. 국내 대학과 기업 연구자들이 현재 활용할 수 있는 최첨단 장비들이란 얘기다. 삼성전자와 SK하이닉스에서 석·박사 졸업생까지 재교육해야 하는 이유다. 네덜란드 ASML이 독점하고 있는 첨단 EUV 노광장비의 대당 가격은 2000억원, 부동산 세수 증가 여유 덕분에 국민 88%에게 수십만원씩 나눠준다는 5차 재난지원금의 규모는 15조 7000억원이다.

![애나 키우라는 시모…"나쁜 며느리 돼라" 정신과 의사가 깨달은 것 [마흔공부⑤]](https://pds.joongang.co.kr/news/component/htmlphoto_mmdata/202404/20/66ac3767-cd4b-4fdf-a568-90fd486a334f.jpg.thumb.jpg/_ir_432x244_/aa.jpg)